用突發脈沖器準確分析脈沖抗擾度

本文重點分析電子系統抗干擾路徑時的物理問題。詳細請下載:如何用突發脈沖發生器準確分析脈沖抗擾度?

一、引言

今天,在最先進的電子電路中找到故障正變得越來越難。除了更加復雜(并且因此一些高得多的潛在故障源),小機械尺寸讓開發人員越來越難查明故障。下面是北京海洋興業科技股份有限公司進行測量的例子。

二、任務

一個新的控制單元是干擾發生器抗擾度試驗檢查的對象。該控制單元電路板包括液晶顯示器(+控制器)、μC(142引腳TQFP)、FPGA(100引腳TQFP)、接口模塊、無源器件(如SMD 0603)和各種控制元件(旋轉編碼器、按鈕、開關)。此外,在電路板承載的USB插座,連接器用于將隨后由發生器和電源輸入來產生的電壓。由于成本原因,電路板被設計成具有200微米特征尺寸的雙層系統。沒有連續的GND層。該總線/線放在兩個層次。控制單元向發生器單元的接近導致高抗干擾要求。

根據DIN EN 61000-4-2,功能故障發生在第一次ESD測試中。干擾脈沖(接觸放電)連接到電路板的接地系統后,微控制器出現故障,通過跳動信號故障和定格顯示變得明顯。這種故障發生在不同的電壓(2.4kV-4kV)取決于靜電槍的位置(連接點和角)。顯然抗擾水平必須提高。

三、耦合機制

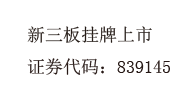

如圖1所示是兩種電電位耦合機制,通過該干擾可能到達電路板重要區域:磁耦合和電耦合。

當使用ESD靜電槍耦合擾動到模塊時,區別在:磁耦合期間,干擾電流流過電路板,并產生磁性,這反過來又可能在導體回路感應電壓。這些電壓可能導致兩種不同類型的問題:感應電壓既可以視為由該電路的輸入邏輯信號,又可視為它驅動擾動電流,這會在控制電路的其它部分引起問題。

電耦合也可引起干擾。電場電容耦合到電路板的線路網絡或組件。所得位移電流可能反過來以兩種不同的方式影響系統:位移電流可能導致在電阻器上的電壓降(反抗VSS或VDD),這再次被認為是一個邏輯信號,或在類似于磁耦合引起的電路其他部分感應電壓。

干擾必須被施加到選擇的各個線路(例如,在總線系統)和/或它們的通孔或單個IC引腳以查明易敏感模塊組件。在微米范圍內的電路和特征尺寸的一體化的上述高層導致對干擾源的機械分辨率越來越高的要求。

由于功能故障和抗擾水平知道,合適的可能性必須找到以提高系統的抗干擾性能。在合規測試中,故障范圍可能縮小到控制器。但它仍然必須確定它的精確引腳是完全負責事故。這是絕對必要的,因為沒有適當的反制措施(阻塞IC引腳,掩蓋易敏感線)本來可以有效地采取。

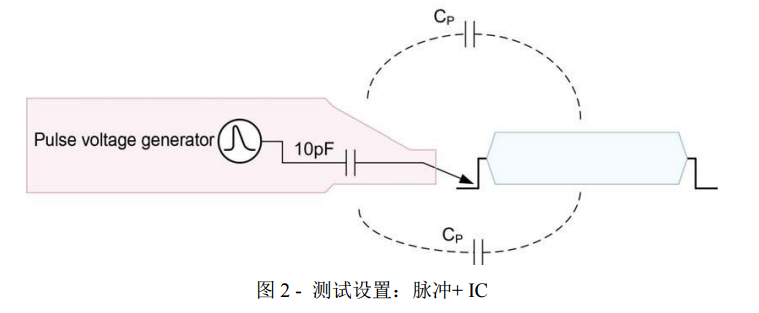

一種類似ESD干擾不得不被單獨地應用到每個引腳來識別易敏感線/ IC管腳。ESD靜電槍不能再使用有以下幾個原因:1、對于單個IC引腳,這些脈沖太強,這很容易損壞電路。2、由ESD靜電槍發出的場可以影響電路的其他部分,從而阻礙顯著具體的故障定位。3、機械尺寸使它幾乎是不可能的連接到個別引腳無短路鄰近的引腳。4、由于線密度,有受限接入到地面系統周圍的電路使得難以連接到基準線。

四、路徑

E或B場源常常用于局部注入干擾。但是,在目前的情況下其選擇性是不充分的,并且使它們更小似乎是不明智的。這將大大減少在E場源的電極和相應的電路板結構/元件包之間的耦合電容,以致于所得的干擾脈沖不足以產生被之前注意到的故障。

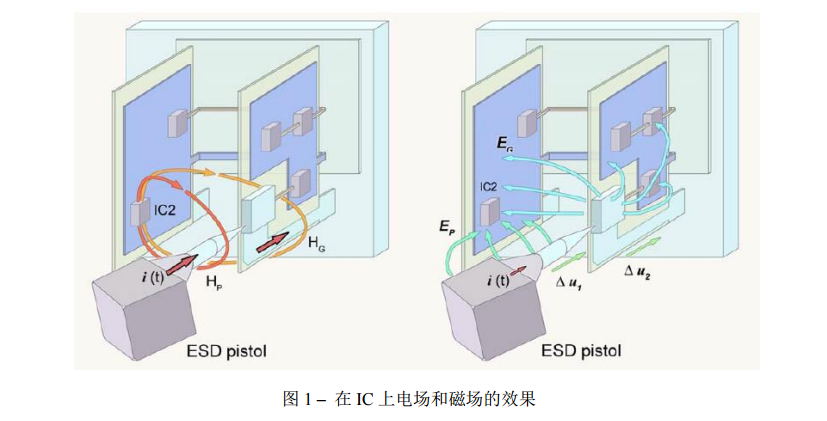

開發一種新的干擾發生器來避免這個問題。它產生邊沿陡峭的干擾脈沖(1.2kV/1.8

ns上升時間),它可以通過內部電容(10

pF)耦合到被測設備中。可以調節極性和強度。例如,可更換的針電極被用于連接引腳。

這一原理有幾個優點:1、要施加到該干擾具有結構之間的耦合電容和場源總是相同(不再取決于距離)。2、高度集成的電路封裝(TQFP)的引腳可以單獨地連接。3、與小結構相對的耦合電容增加。4、電路可以在應用程序進行測試。

由于在附近的一個真正的測試模塊的信號,連接到脈沖發生器沒有足夠短接地是可行的,設計發生器以致使耦合到測試設備的電容是足夠的。場源的脈沖形狀最早在50Ω系統檢查,用1GHz示波器,以確保由脈沖電壓源產生的干擾足夠大來干擾系統。

測量表明,產生的8 V脈沖是強到足以引起與IC的干擾,盡管電容電流返回路徑(振幅和曲線形狀取決于測量裝置,例如,干擾被注入高阻抗的輸入或驅動器輸出)。干擾脈沖逐一施加到這種測量設置的每個IC引腳。最低脈沖頻度最初選擇在正極性。在第一次測試時,無功能故障可能被發現。之后逐漸增加頻度,如與ESD靜電槍合規測試同樣的故障模式出現了。控制器可以作出由耦合到20線路中的2條線路引起的事故,這通向控制單元。只有兩個修改最初認為是潛在的應對措施:對地阻塞電容器的安裝和芯片電感的安裝/在控制單元和控制器之間的線電阻。安裝兩個10 pF的0402電容后,P23又被應用到所有引腳。該故障并沒有重新出現。

然后用ESD靜電槍的合規測試重復。很明顯,導致在兩個測試的故障是相互關聯的,抗擾能力提高到4.8kV。

五、 結論

設備抗擾度測試期間發生的干擾可以模擬,并且特別敏感的電路部件(IC引腳/線路)可以通過局部耦合成單獨的線或IC的引腳進行標識。分析故障原因變得更容易,并且開發人員可以得到一個底部的故障要快得多。

參考文獻

[1] "Neue Aspekte zur ESD-St?rfestigkeit“ Elektronik, 05/2009, Author: Gunter Langer

[2] "Neue Burst-Generatoren zur Prüfung der St?rfestigkeit von integrierten Schaltungen“,2004, Author: Gunter Langer, Bernd Deutschmann & Günther Auderer

@本文屬于北京海洋興業科技股份有限公司所有,如需轉載,請注明出處。